在研发阶段取得试产品:晶圆/芯片后,大多必须透过封装工艺,才能进行后续的芯片检测分析。

而近期宜特观察到,越来越多客户,特别是学术研究单位,找上宜特进行工程验证时,会先寻求宜特协助进行「工程样品快速封装」; 最大原因就在于大型封装厂处理量产品已应接不暇,学术研究单位需要的少量研发工程样品封装需求,无法承接,因此找上宜特寻求协助。

为了可以让客户与学研单位拿到工程封装品,宜特在20多年前即已成立快速封装实验室,每年替半导体客户、学术研究单位完成数十万颗实验性工程封装IC样品。

本期宜特小学堂,将与您分享,宜特快速封装实验室,实际上是如何运作,让您顺利拿到工程封装样品;特别是针对系统级构装((System in Package,简称SiP)、多芯片模块(Multi Chip Module,简称MCM )、四方平面无引脚封装(Quad Flat No-Lead,简称QFN)等特殊封装形式在进行故障分析前的样品前处理,快速封装服务如何派上用场,克服测试瓶颈。

一、透过宜特公板封装,快速取得工程样品

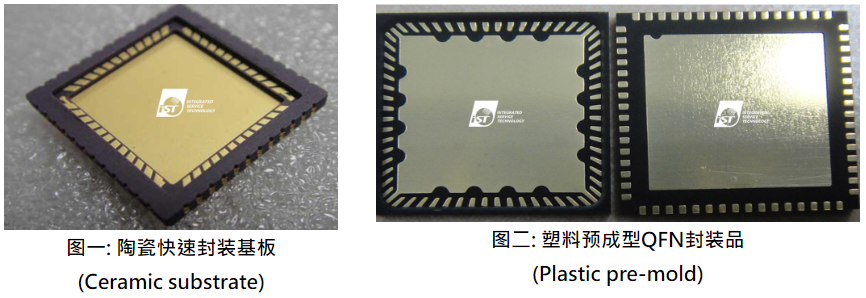

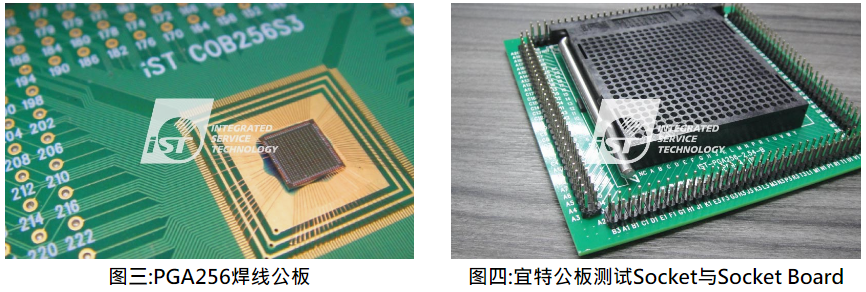

传统量产品的封装多使用导线架(Lead frame)与载板(Substrate),封装工艺多达20-30道,交期从3天到数周不等。而针对实验性的工程样品,宜特快速封装实验室则是透过陶瓷(参见图一)、塑料预成型(Plastic Pre-mold)(参见图二)等材料,或公版COB/Socket整合样品制作(参见图三、图四),精简工艺只需4道(参见图五)。

值得一提的是,目前芯片封装多以焊线验证前提下,宜特公板结合共享与整合性测试环境的优势,提供包含48/64/256等脚数规格(图三、图四),简易完成可供验证的样品,快速进行功能验证。

首先,第一步是封装焊线图确认。您可以提供封装厂的焊线图,或是将芯片数据提供给宜特,宜特将选用适合规格材料后,绘制出封装焊线图,确认无误即可进行正式样品作业。接着,依据客户需求,使用导电或非导电胶,黏贴芯片在封装材料上,再依照芯片规格,选用适当线材、线径进行焊线作业。

最后因应客户测试或使用方式,宜特可提供玻璃盖、陶瓷盖或是使用封胶方式保护芯片与焊线,即可让您取得封装样品,供后续工程验证使用。

二、 多芯片封装验证神助功:IC Repackage移植技术

当IC发生defect时,想分析其中一颗组件的异常状况,又碍于SiP、MCM、MCP、BGA内部打线或基板线路互联的关系,将导致电性测试时,容易受到其他Chip或组件影响,造成判定困难,甚至无法判定。

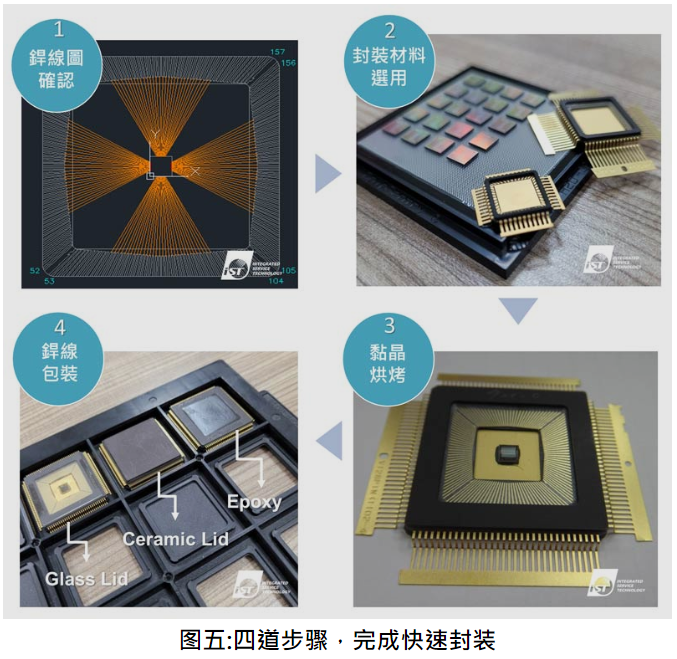

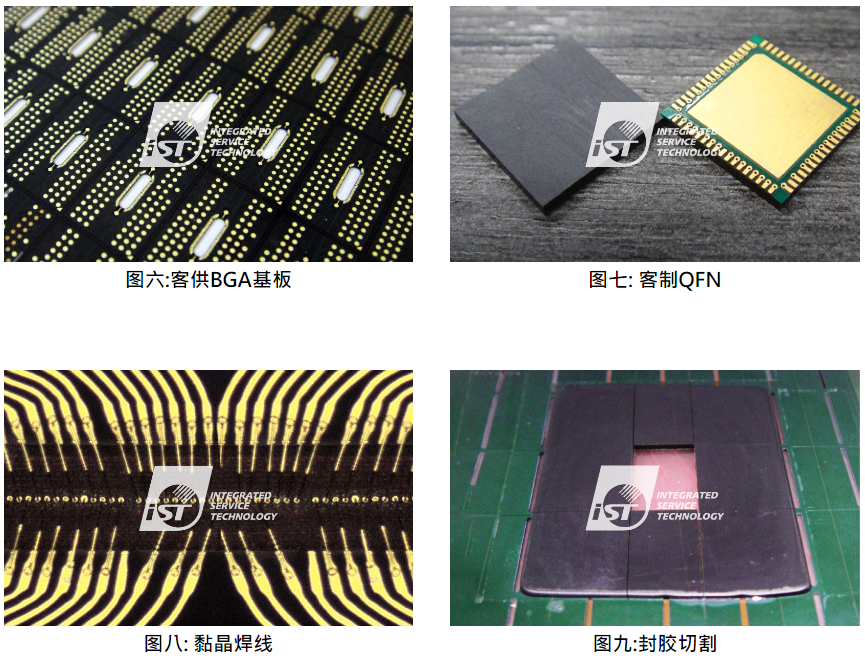

透过宜特研发出IC Repackage移植技术,可将SiP、MCM、MCP、BGA等封装体里头,欲受测Die移植出来,送至宜特快速封装实验室,透过您提供的基板(客供基板,图六)、或是由宜特协助您客制基板(图七),进行重新黏晶焊线(图八)及封胶切割/植球(图九)成您所要求的Package型式,即可进行后续各式电性测试(阅读更多: IC Repackage移植技术 助先进封装芯片检测无碍)

三、复杂封装工程样品,如何进行样品前处理?

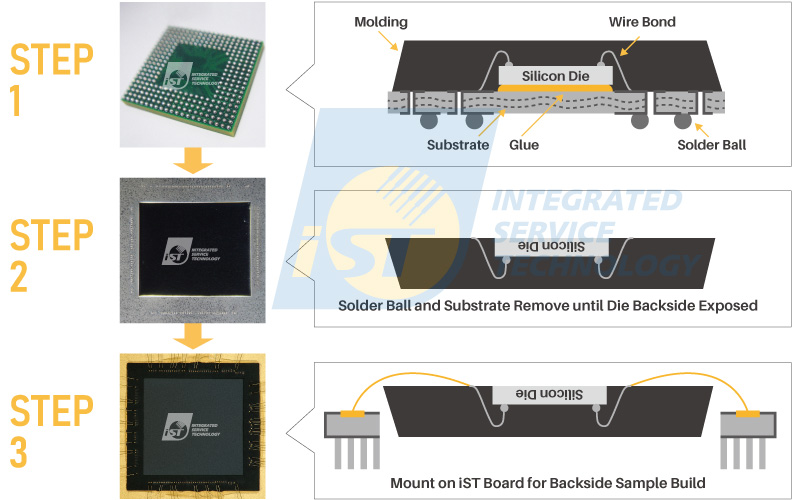

IC设计要进行后续功能性测试、可靠度测试或故障除错前,必须针对待测样品做处理。而样品前处理的技术,对于后续功能测试是否准确、缺陷是否容易找到,都扮演关键性重要角色。传统样品前处理手法不外乎是透过IC开盖(Decap)或研磨 (Front-side Polish )手法;从封装体(Package)正面透过化学/雷射蚀刻(Chemical/Laser de-capsulation)露出正面,或胶体背面研磨至芯片裸露,或如前段提及,透过取Die进行Repackage移植的样品前处理方式,

不过,在封装线材日渐复杂的状况下,重新焊线的风险提高,原始封装的芯片焊垫经过化学蚀刻后将更为脆弱.后续故障分析也会因芯片结构层数过多,需要由晶背来厘清的比例增加。

宜特快速封装实验室也可藉由协助您,移除阻碍背面观测的基板,并以桥接的方式,将指定位置焊点引线出来后,再透过EFA设备,从晶背得到清晰异常位置,进一步定位进行分析。

1830次

1830次 2023-03-10

2023-03-10